- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

### DfX – Defect Universe & test coverage

They design defects, They manufacture defects, They sell defects. What about you?

Christophe LOTZ

christophe.lotz@aster-technologies.com

TEST FORUM 2013

Nov 26-27, 2013, Tallinn, Estonia

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

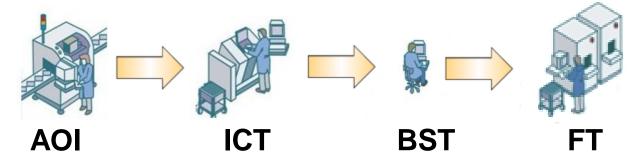

## Design and production changes

Staggering board density.

Outsourcing of board assembly.

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

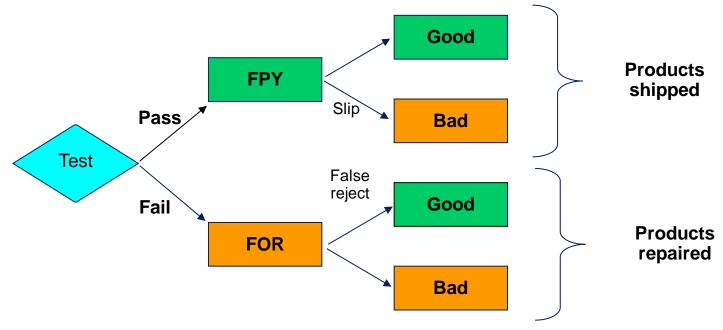

### We buy good boards

- \$\bigsip\$ Is a board good because it passes the test?

- What is the acceptable percentage of faulty boards that could be delivered with the "good boards" label?

A man with one watch knows what time it is.

A man with two watches is never sure.

Coverage must be readable from design to production: Unified metrics to compare & combine.

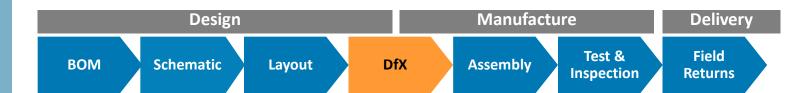

### **Design For Excellence**

♦ Traditional Workflow: Expensive and Longer.

TestWay - A unique dedicated workflow from Design to Delivery, where DfX is distributed.

#### **Test Forum 2013**

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

### **Good products**

- Good products must be defect-free at minimum cost.

- How to detect or prevent all faults on the product so that only good products are shipped?

**Defect Prevention**

**Defect Detection**

Test coverage is a key metric as it will be the quality warranty and the main driving factor for LeanTest.

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

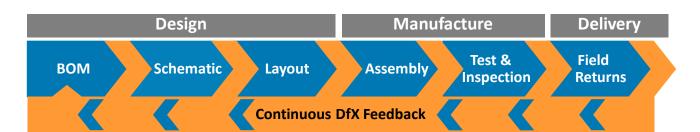

### **Defect Universe**

In order to consider all defects including design validation and testing, we need 3 main defect classes:

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

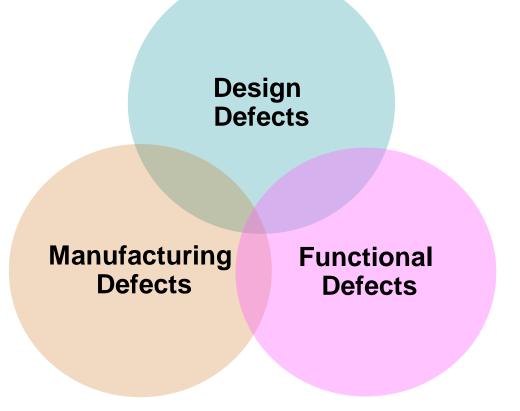

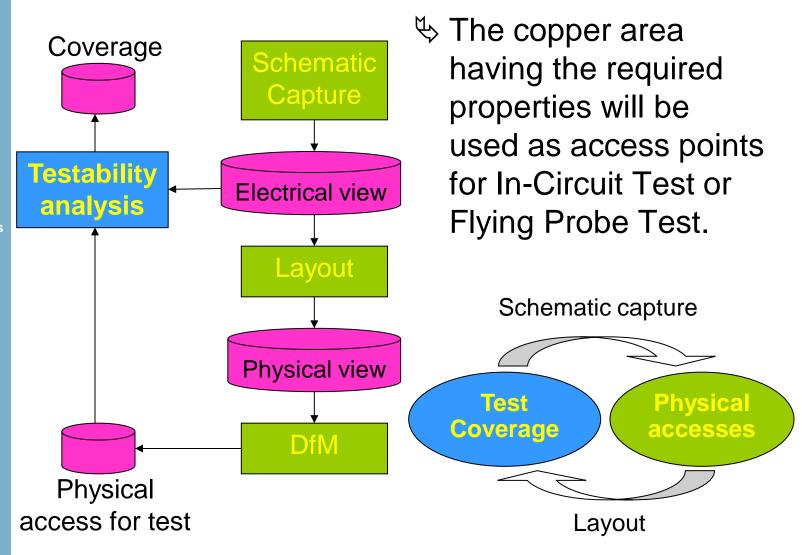

### Schematic - Electrical DfT

Design and Testability rules violations limit test coverage.

Accessibility

requirements are back

annotated prior to

layout, ensuring that

the required physical

accesses will be

available where they

are mandatory.

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

### **Layout – Mechanical DfT**

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

### **Test Coverage**

- Demonstration using an absurd example

- ✓ Board 4 components: 3 resistors, 1 BGA.

- ✓ The 3 resistors are measured with very high accuracy.

- ✓ No test on the BGA.

- ✓ Is the board test score really 75%?

3 resistors / 4 components

- ✓ We need something to weight the coverage...

It must be credible, easy to update to reflect growing electronics complexity.

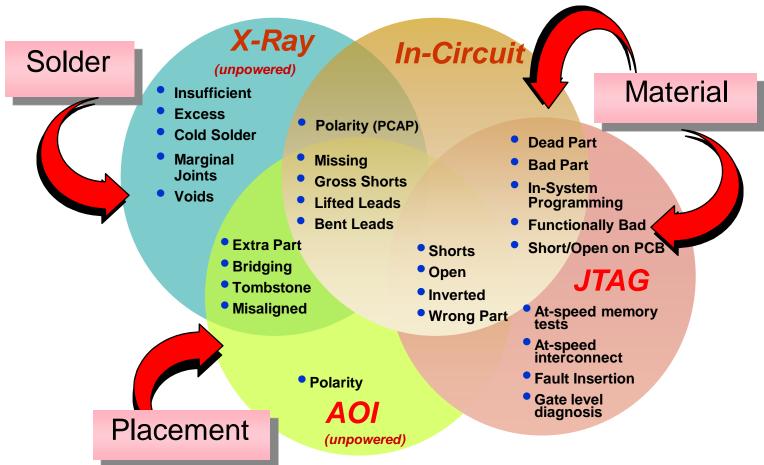

## **Manufacturing Defect Universe**

Use Identify the faults that can occur.

### Test Forum 2013

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

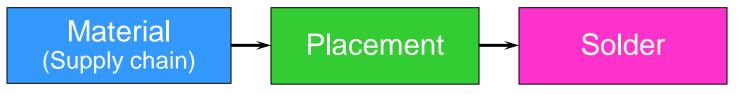

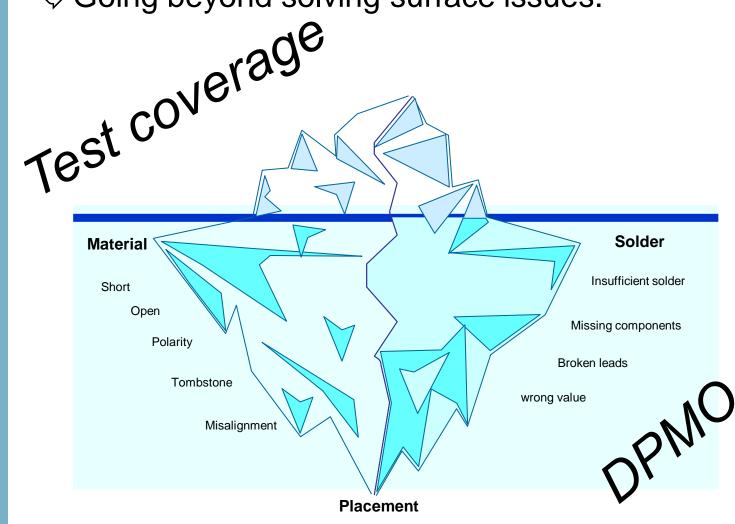

# Manufacturing Defect Universe

♦ Typical manufacturing defects:

Missing components

Incorrect Polarity

Misalignment

Open Circuits

Wrong value

**Broken** components

Short circuits

**Tombstone**

Insufficient solder

Excessive solder

We need to group defects into categories, to understand what defects can be captured by a particular test strategy.

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

### **Test coverage**

- The ability to detect defects can be expressed with a number: coverage.

- \$\Box\$ Each defect category fits with its test coverage:

| MPSF [1]  | PPVSF    | PCOLA/SOQ /FAM |

|-----------|----------|----------------|

| Material  | Value    | Correct        |

|           |          | Live           |

| Placement | Presence | Presence       |

|           |          | Alignment      |

|           | Polarity | Orientation    |

| Solder    | Solder   | Short          |

|           |          | Open           |

|           |          | Quality        |

| Function  | Function | Feature        |

|           |          | At-Speed       |

|           |          | Measure        |

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

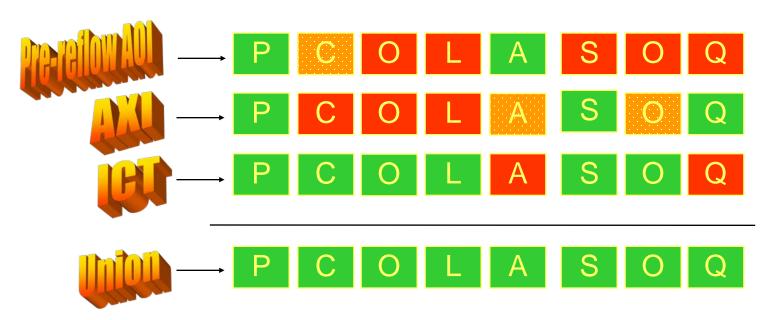

## Test coverage by defect category

- Each test technique brings a certain ability to capture the defect universe.

- No single solution is capable of detecting all the defects.

♦ Good coverage = combination of tests.

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

## Test coverage by defect category

♣ For each category (Material, Placement, Solder) of defects (D), we associate the corresponding coverage (C).

$$\text{Effectiveness} = \frac{\sum D_{\text{M} \times} C_{\text{M} +} \sum D_{\text{P} \times} C_{\text{P} +} \sum D_{\text{S} \times} C_{\text{S} +} \sum D_{\text{F} \times} C_{\text{F}}}{\sum D_{\text{M} +} \sum D_{\text{P} +} \sum D_{\text{S} +} \sum D_{\text{F}}}$$

The test efficiency is based on a coverage balanced by the defect opportunities.

We need a better coverage where there are more defect opportunities!

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

## Faulty boards at system level

Electronic plants, in charge of board integration, often discover a significant amount of defective boards at system test.

- How is it possible to get failures at system level if we only buy good boards?

- ? The defect appears during packing and transportation (vibration, extreme temperatures, moisture).

- ? The defect is a dynamic problem which is revealed by the integration of the board in the complete system.

- ? The reality is usually more simple...

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

## Faulty boards at system level

♦ If the board is failing at system test, it is usually because the escape rate (or slip) is higher than expected.

- ♦ There are only two possibilities:

- ✓ The combined coverage is lower than optimal.

- ✓ The DPMO figures are higher than expected.

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

### Faulty boards at system level

- The auditing conclusions were:

- ✓ Wrong or inadequate coverage metrics are produced: Example: confusion between accessibility and testability; coverage by component only - without incorporating solder joint figures; Over optimistic report (marketing driven report),

- ✓ Wrong DPMO figures, due to limited traceability or incorrect root cause analysis (Example: confusion between fault message and root cause/defect).

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

### **DPMO** estimation

\$\to\$ Going beyond solving surface issues.

- Introduction

- Good products

- Defect Universe

- Design Defects

- Manufacturing Defects

- Test Coverage

- Test efficiency

- Faulty boards

- Conclusion

### Conclusion

- From design, during production and in a more general way, through the whole life cycle, coverage estimation permits the test process to be optimized.

- By deploying various testers in the best order, at the best time, with controlled levels of redundancies, costs can be reduced and quality levels raised.

- The economic challenges are critical: the tools to meet them are available

### Contact

### **ASTER Technologies**

55 bis, rue de Rennes

35510 CESSON-SEVIGNE - FRANCE

Contact: Christophe LOTZ

Tel: +33 (0)299 83 01 01

E-mail: <u>sales@aster-technologies.com</u>

Web: <u>www.aster-technologies.com</u>

Our local distributor, POTEQ is an exhibitor at TestForum!

Thank You