# **JTAG Technologies**

Interactive Debug of CPU and Peripheral hardware via 1149.1 Port.

Emulative Test & Programming (ETP)

21/11/2013

TCK

21/11/2013

TCK

### ETD in ad

## **ETP** in addition to Boundary-Scan

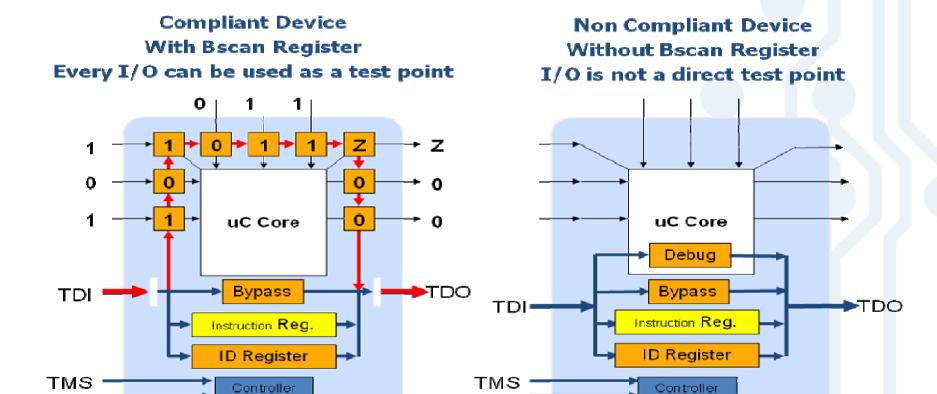

- ETP can help to increase the fault coverage by:

- covering nets not accessible via a boundary-scan register

(eg no bscan reg available, or no access to certain signals from bscan reg)

21/11/2013

- covering at-speed errors in high frequency links

- ETP can (sometimes) help to increase the performance when needed (eg flash progr)

- ETP can assist the hardware engineer with (prototype) hardware debugging

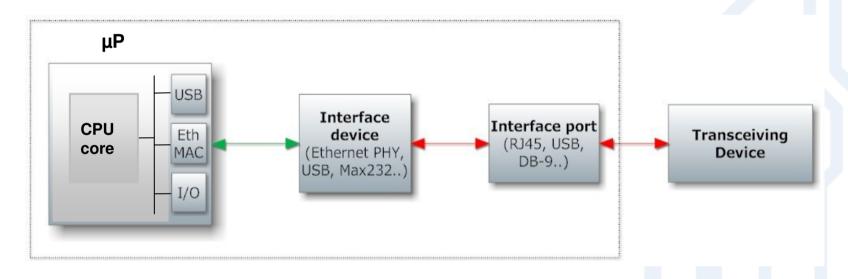

## **μP-based Designs**

Test connections between  $\mu P$  / peripheral controllers and connected peripheral logic (at-speed)

# Using ETP for µP-based Designs

- ETP provides the capability to instruct the CPU core to execute individual RD and WR cycles at-speed

- ETP facilitates (at-speed) testing and debugging of the connections / communication between the CPU and its system devices:

- Memory

- Peripherals and "beyond"

- Peripheral controllers and connected peripherals and "beyond"

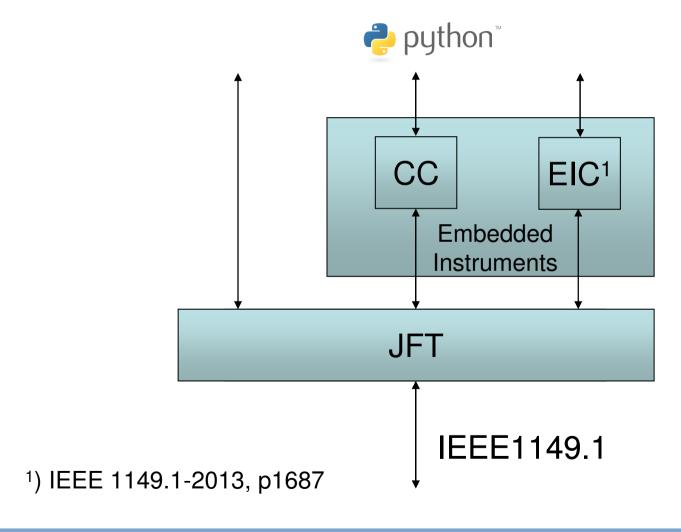

## **ETP using JTAG Functional Test**

#### WWW.ITAG.COM

### Case Study – DDR testing via CoreCommander 1

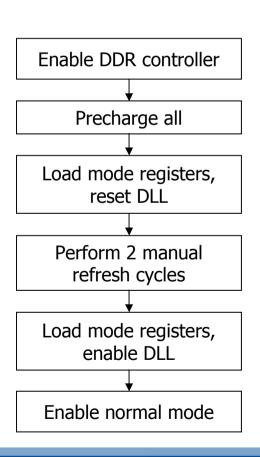

- Correct functional access to DDR from processor requires proper initialization

- Processor and bus clock -> also determines DDR clock speed

- DDR parameters

- number of row and column addresses

- burst length

- latency

- data width

- -> some of these have to be set for both DDR and DDR controller

### **Case Study – DDR testing via CoreCommander 2**

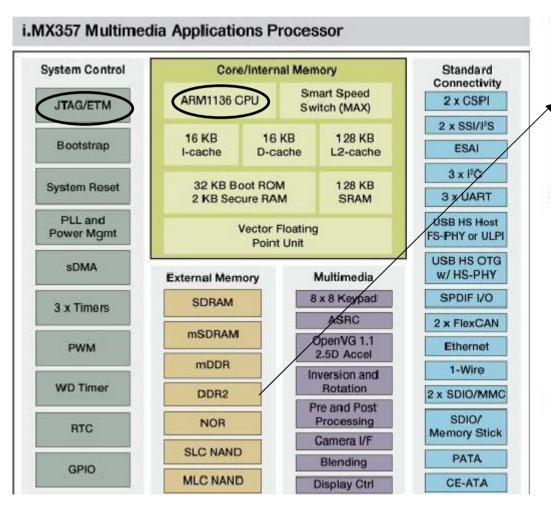

Enhanced SDRAM controller (ESDRAMC)

Up to 2 chip selects (due to sharing of pins, 2 chip selects are supported only when the WEIM CS2 and CS3 are not is use).

Support x32/x16 SDR SDRAM (up to 2 Gb@133 MHz)

Support x32/x16 LPDDR SDRAM (up to 2 Gb@266 MHz)

# **Case Study – DDR testing via CoreCommander 3**

Setting up DDR Controller – Code

```

def InitDDR ():

jftuproc.WriteMemory (SDRAM_CONTROL_ESDMISC, 0x244)

jftuproc.WriteMemory (SDRAM_CONTROL_ESDMISC, 0x24C)

# Enable DDR

# Enable DDR, Reset Delay line

iftuproc.WriteMemory (SDRAM CONTROL ESDCFG1. 0x0076E83F) # set timing

iftuproc.WriteMemory (SDRAM_CONTROL_ESDCTL1. 0x92210080) # set Precharge ALL mode

jftuproc.WriteMemory8 (DDR_BASE_1 + 0x400, 0xDA)

# start precharge all.

# use 8 bit access !!!!!!!!!!

iftuproc.WriteMemory (SDRAM CONTROL ESDCTL1. 0xB2210080) # select Load Register Mode

jftuproc.WriteMemory8 (DDR_BASE_1 + 0x2000000, 0xda) # Load MR2

jftuproc.WriteMemory8 (DDR_BASE_1 + 0x3000000, 0xda) # Load MR3

jftuproc.WriteMemory8 (DDR_BASE_1 + 0x1000400, 0xda) # Load MR1, enable DLL

jftuproc.WriteMemory8 (DDR_BASE_1 + 0x0000333, 0xda) # Load MR0, reset DLL

jftuproc.WriteMemory (SDRAM_CONTROL_ESDCTL1, 0x92210080) # set Precharge ALL mode

# start precharge all

# use 8 bit access !!!!!!!!!!

jftuproc.WriteMemory8 (DDR_BASE_1 + 0x400, 0xDA)

jftuproc.WriteMemory (SDRAM_CONTROL_ESDCTL1, 0xA2216080) # set MANUAL REFRESH mode

jftuproc.WriteMemory8 (DDR_BASE_1, 0xDA)

jftuproc.WriteMemory8 (DDR_BASE_1, 0xDA)

# start refresh

# start refresh

jftuproc.WriteMemory (SDRAM_CONTROL_ESDCTL1, 0xB2210080) # select Load Register Mode

jftuproc.WriteMemory8 (DDR_BASE_1 + 0x0000233, 0xda)

jftuproc.WriteMemory8 (DDR_BASE_1 + 0x1000780, 0xda)

# Load MR0, end reset DLL

# Load MR1, OCD default

jftuproc.WriteMemory8 (DDR BASE 1 + 0x1000400. 0xda)

# Load MR1. OCD exit

iftuproc.WriteMemory (SDRAM_CONTROL_ESDCTL1. 0x82226080) # select Normal operation mode

# 200 cycles needed

DDR DELAY LINE = 0x00F49F00

(SDRAM_CONTROL_ESDCDLY1, DDR_DELAY_LINE) # set delay line to suggested val

(SDRAM_CONTROL_ESDCDLY2, DDR_DELAY_LINE) # set delay line to suggested val

(SDRAM_CONTROL_ESDCDLY3, DDR_DELAY_LINE) # set delay line to suggested val

(SDRAM_CONTROL_ESDCDLY4, DDR_DELAY_LINE) # set delay line to suggested val

(SDRAM_CONTROL_ESDCDLY5, DDR_DELAY_LINE) # set delay line to suggested val

jftuproc.WriteMemory

jftuproc.WriteMemory

jftuproc.WriteMemory

jftuproc.WriteMemory

iftuproc.WriteMemory (

#### end init DDR

```

### **Conclusions**

- Emulative Test and Programming

- Simple control over CPU no code needed

- Increase fault coverage

- When no or restricted BSCAN register

- At Speed tests in high frequency links

- Increase Performance of Flash programming

- Structural Test is still relevant and alive

We are boundary-scan.

21/11/2013